Exemple:  $2 \text{ GHZ}=2*10^9 = 2\ 000\ 000\ 000\ IMP/Sec$

2 Milliards d'IMP/Sec

• Les processeurs 'C6211, 'C6701, 'C6201 et 'C6202 travaillent respectivement a des fréquences de 150, 167, 200 et 250 MHz.

## 3.2 Le processeur

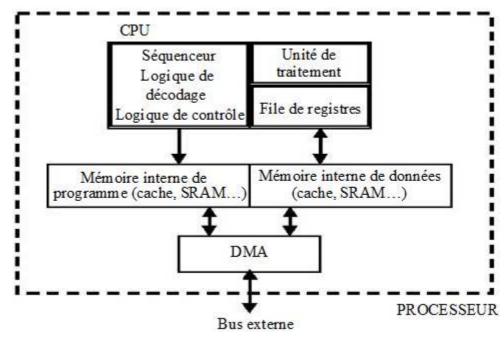

La plateforme TMS320C6000 des processeurs de signaux numériques fait partie de la famille TMS320. Elle comporte les processeurs TMS320C62x à arithmétique fixe et TMS320C67x à arithmétique flottante. Afin de bien comprendre le fonctionnement des DSP, il faut voir ce processeur comme un ensemble de blocs interconnectés (voire **Figure 3.2**).

Les principales caractéristiques d'un DSP "TMS320Cx" sont:

- ✓ Les architectures de ces processeurs sont Harvard (mémoire de programme et mémoire de données séparées) et VLIW (Very Long Instruction Word) d'ordre 8, c'est-a-dire qu'ils sont capables d'exécuter jusqu'a 8 instructions 32-bits en parallèle par 8 unités fonctionnelles.

- ✓ Le CPU (Central Process Unit) est constitue de 32 registres généraux de 32-bits, et de 8 unîtes de traitement, 2 multiplieurs et 6 ALU (Arithmétique and Logic Units).

- ✓ DMA (Direct Memory Access) : 4/16 channels : Elle permet de faire des transferts des données sans passer par le CPU.

- ✓ Une EMIF (External Memory Interface): Glueless access to async/sync memory EPROM, SRAM, SDRAM, SBSRAM: Elle permet de faire l'interfaçage entre les différents types de mémoire externe et le DSP.

Figure 3.2. L'organisation en blocs d'un DSP basé sur une architecture VLIW et Harvard.

## 3.3 Architecture interne du C6000

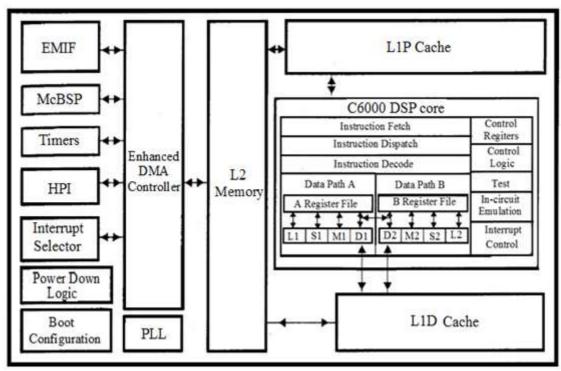

Le détail de l'architecture interne du DSP basé sur le cœur C6000 (dont est dérive le C6x) est représenté dans la **figure 3.2**.

Figure 3.2. Schéma fonctionnel de TMS320C6x.

Le DSP TMS320C6000 intègre un CPU (Central Processing Unit) des mémoires internes de programme et de donnée, des bus internes de programmes et de données et des périphériques internes.

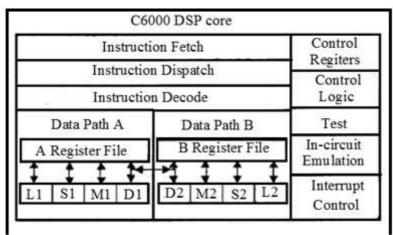

- Le cœur C6000 qui est représente dans la **figure 3.3**, possède :

- ✓ Une unité de chargement de programme (programme Fetch) ;

- ✓ une unité de répartition des instructions (Instruction Dispatch) ;

- ✓ une unité de décodage des instructions (Instruction Decode) ;

- ✓ 32 registres de 32- bits séparent en deux fois 16 registres (A Register File et B Register File);

- ✓ deux voies pour les données (data path) contenant chacune quatre unités de traitement (L, S, M, D);

- ✓ deux registres de contrôle (Control Regiters);

- ✓ une logique de contrôle (Control Logic);

- ✓ Test, In-circuit Emulation, Interrupt Control;

- ✓ Les unîtes exécutent des instructions logiques, de décalage (Shifting), des multiplications hardwares et des opérations sur les adresses de données. Tous les transferts de données entre la file de registre et la mémoire se font exclusivement par les unîtes « Data adressing».

- ✓ Les quatre chemins sont croises, ce qui permet l'échange de données entre les deux files de registre.

- Les périphériques sur puce comprennent deux ports sériés multicanaux à mémoire tampon (**McBSP**) (two multichannel buffered serial ports), deux minuteries (two timers), une interface de port hôte 16 bits (**HPI**) (Host Port Interface) et une interface de mémoire externe 32 bits (**EMIF**) (External Memory Interface). Il nécessite 3,3 V pour les E/S et 1,8 V pour le noyau (interne).

**Figure 3.3** le cœur C6000.

- Les bus internes comprennent un bus d'adresses de programme 32 bits, un bus de données de programme de 256 bits pour recevoir huit instructions de 32 bits, deux bus d'adresses de données de 32 bits, deux bus de données de 64 bits et deux bus de données de stockage de 64 bits. Avec un bus d'adresse 32 bits, l'espace mémoire total est de 232 = 4 GB, y compris quatre espaces mémoire externes: CE0, CE1, CE2 et CE3. La figure 3.3 présente un schéma fonctionnel du processeur C6711 inclus avec CCS.

- Les banques de mémoire indépendantes sur le C6x permettent deux accès mémoire en un cycle d'instruction. Deux banques de mémoire indépendantes sont accessibles via deux bus indépendants. La mémoire interne étant organisée en banques de mémoire, deux instructions de chargement ou de stockage peuvent être exécutées en parallèle. Aucun conflit ne se produit si les données consultées se trouvent dans différentes banques de mémoire. Des bus distincts pour les programmes, les données et l'accès direct à la mémoire (DMA) (Direct Memory Access) permettent au C6x d'exécuter simultanément des opérations d'extraction de programmes, de lecture et d'écriture de données et d'opérations DMA. Avec des données et des instructions résidant dans des espaces mémoire séparés, des accès mémoire simultanés sont possibles. Le C6x dispose d'un espace mémoire adressable sur des octets. La mémoire interne est organisée en espaces de mémoire de programme et de données séparés, avec deux ports internes 32 bits (deux ports 64 bits avec le C64x) pour accéder à la mémoire interne.

- Avec une horloge de 150 MHz à bord du DSK, on peut atteindre idéalement deux multiplications et accumuler par cycle, pour un total de 300 millions de multiplications et accumulations (MAC) par seconde. Avec six de huit unités fonctionnelles de la figure 3.2 (et non les unités .D décrites ci-dessous) capables de gérer des opérations en virgule flottante, il est possible d'effectuer 900 millions d'opérations en virgule flottante par seconde (MFLOPS) (Million PLoating-Point Operations Per Second). Fonctionnant à 150 MHz, cela correspond à 1200 millions d'instructions par seconde (MIPS) (Million Instructions Per Second) avec un temps de cycle d'instructions de 6,67 ns.